QMP 7.1 D/F

## Channabasaveshwara Institute of Technology

(Affiliated to VTU, Belgaum & Approved by AICTE, New Delhi) (ISO 9001:2015 Certified Institution) NH 206 (B.H. Road), Gubbi, Tumkur – 572 216. Karnataka.

## Department of Artificial Intelligence and Data Science MICROCONTROLLER AND EMBEDDED SYSTEMS PRACTICAL COMPONENT OF IPCC

(Academic year 2022 - 2023)

SEMESTER – IV

# 21CS43

Lab Manual

Name :\_\_\_\_\_

USN :\_\_\_\_\_

Batch :\_\_\_\_\_\_\_ Section : \_\_\_\_\_\_

CHANNABASAVESHWARA INSTITUTE OF TECHNOLOGY

(Affiliated to VTU, Belgaum & Approved by AICTE, New Delhi) (ISO 9001:2015 Certified Institution) NH 206 (B.H. Road), Gubbi, Tumkur – 572 216. Karnataka.

DEPARTMENT OF ARTIFICIAL INTELLIGENCE AND DATA SCIENCE

## LABORATORY MANNUAL

## Microcontroller and Embedded Systems Laboratory/21CS43

(Effective from the academic year 2022 -2023)

Channabasaveshwara Institute of Technology

(Affiliated to VTU, Belgaum & Approved by AICTE, New Delhi) (ISO 9001:2015 Certified Institution) NH 206 (B.H. Road), Gubbi, Tumkur – 572 216. Karnataka.

DEPARTMENT OF ARTIFICIAL INTELLIGENCE AND DATA SCIENCE

## SYLLABUS

### MICROCONTROLLER AND EMBEDDED SYSTEMS [PRACTICAL COMPONENT OF IPCC]

### SEMESTER - IV

Subject Code: 21CS43

Number of Lecture Hours/Week: 03 L + 02 P

Total Number of Contact Hours: 40T +20 P

CIE Marks: 50 SEE Marks: 50 Exam Hours: 03

CREDITS – 04

Course Learning Objectives: This course (21CS43) will enable students to:

CLO 1: Understand the fundamentals of ARM-based systems, including programming modules with registers and the CPSR.

CLO 2: Use the various instructions to program the ARM controller.

CLO 3: Program various embedded components using the embedded C program.

CLO 4: Identify various components, their purpose, and their application to the embedded system's applicability.

CLO 5: Understand the embedded system's real-time operating system and its application in IoT.

## **Programs List:**

### <u>PART A</u>

Conduct the following experiments by writing program using ARM7TDMI/LPC2148 using an evaluation board/simulator andsoftware tool.

- 1. Sample Programs using Keil Compiler

- 2. Write a program to find the sum of the first 10 integer numbers.

- 3. Write a program to find the factorial of a number.

- 4. Write a program to add an array of 16 bit numbers and store the 32 bit result in internal RAM.

- 5. Write a program to find the square of a number (1 to 10) using a look-up table.

- 6. Write a program to find the largest or smallest number in an array of 32 numbers.

- 7. Write a program to arrange a series of 32 bit numbers in ascending/descending order.

- 8. Write a program to count the number of ones and zeros in two consecutive memory locations.

- 9. Display "Hello World" message using Internal UART.

#### PART -B

Conduct the following experiments on an ARM7TDMI/LPC2148 evaluation board using evaluation version of Embedded 'C' & Keil Uvision-4 tool/compiler.

- 1. Interface and Control a DC Motor.

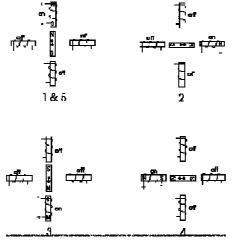

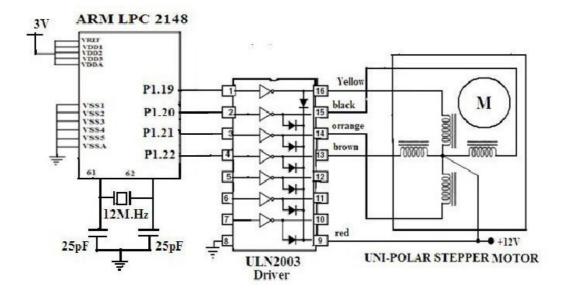

- 2. Interface a Stepper motor and rotate it in clockwise and anti-clockwise direction.

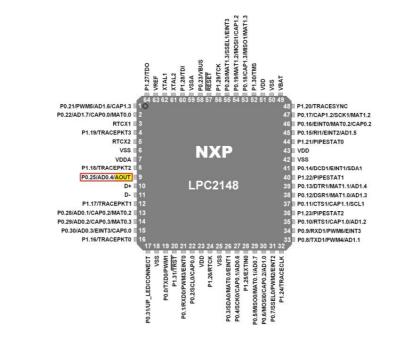

- 3.Determine Digital output for a given Analog input using Internal ADC of ARM controller.

- 4.Interface a DAC and generate Triangular and Square waveforms.

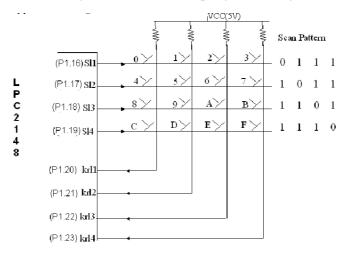

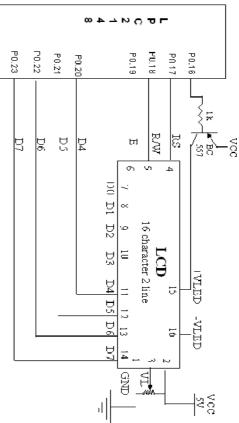

- 5.Interface a 4x4 keyboard and display the key code on an LCD.

- 6. Demonstrate the use of an external interrupt to toggle an LED On/Off.

- 7. Display the Hex digits 0 to F on a 7-segment LED interface, with an appropriate delay in between.

- 8. Demonstration of IoT applications by using Arduino and Raspberry Pi.

## **Course Outcomes**

At the end of the course, the student will be able to:

- CO 1. Explain C-Compilers and optimization

- CO 2. Describe the ARM microcontroller's architectural features and program module.

- CO 3. Apply the knowledge gained from programming on ARM to different applications.

- CO 4. Program the basic hardware components and their application selection method.

- CO 5. Demonstrate the need for a real-time operating system for embedded system applications.

## **Graduate Attributes**

- Engineering Knowledge

- Problem Analysis

- Modern Tool Usage

- Conduct Investigations of Complex Problems

- Design/Development of Solutions

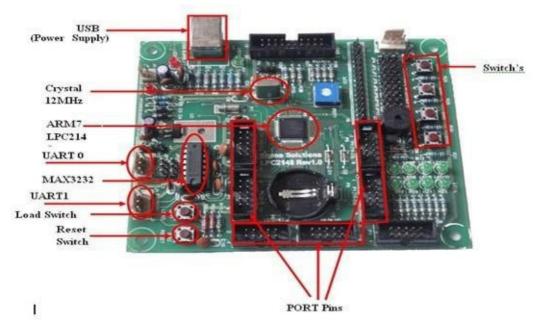

#### ARM7 based LPC2148 Microcontroller

The full form of an ARM is an advanced reduced instruction set computer (RISC) machine, and it is a 32-bit processor architecture expanded by ARM holdings. The applications of an ARM processor include several microcontrollers as well as processors. The architecture of an ARM processor was licensed by many corporations for designing ARM processor-based SoC products and CPUs.

#### LPC2148 Microcontroller

The LPC2148 microcontroller is designed by Philips (NXP Semiconductor) with several in-built features & peripherals. Due to these reasons, it will make more reliable as well as the efficient option for an application developer. LPC2148 is a 16-bit or 32-bit microcontroller based on ARM7 family.

#### Programmer's Model

ARM has a 32-bit data bus and a 32-bit address bus. The data types the processor supports are Words (32 bits), where words must be aligned to four byte boundaries. Instructions are exactly one word, and data operations (e.g. ADD) are only performed on word quantities. Load and store operations can transfer words.

#### Registers

The processor has a total of 37 registers made up of 31 general 32 bit registers and 6 status registers. At any one time 16 general registers (R0 to R15) and one or two status registers are visible to the programmer. The visible registers depend on the processor mode and the other registers (the banked registers) are switched in to support IRQ, FIQ, Supervisor, Abort and undefined mode processing. The register bank organization is shown in below figure. The banked registers are shaded in the diagram.

In all modes 16 registers, R0 to R15, are directly accessible. All registers except R15 are general purpose and may be used to hold data or address values. Register R15 holds the Program Counter (PC). When R15 is read, bits [1:0] are zero and bits [31:2] contain the PC. A seventeenth register (the CPSR - Current Program Status Register) is also accessible. It contains condition code flags and the current mode bits and may be thought of as an extension to the PC. R14 is used as the subroutine link register and receives a copy of R15 when a Branch and

Page No. - 1 -

Link instruction is executed. It may be treated as a general- purpose register at all other times. R14\_svc, R14\_irq, R14\_fiq, R14\_abt and R14\_und are used similarly to hold the return values of R15 when interrupts and exceptions arise, or when Branch and Link instructions are executed within interrupt or exception routines.

| User32   | FIQ32    | Supervisor32 | Abort32  | IRQ32    | Undefined32 |

|----------|----------|--------------|----------|----------|-------------|

| R0       | R0       | R0           | R0       | R0       | R0          |

| R1       | R1       | R1           | R1       | R1       | R1          |

| R2       | R2       | R2           | R2       | R2       | R2          |

| R3       | R3       | R3           | R3       | R3       | R3          |

| R4       | R4       | R4           | R4       | R4       | R4          |

| R5       | R5       | R5           | R5       | R5       | R5          |

| R6       | R6       | R6           | R6       | R6       | R6          |

| R7       | R7       | R7           | R7       | R7       | R7          |

| R8       | R8_fiq   | R8           | R8       | R8       | R8          |

| R9       | R9_fiq   | R9           | R9       | R9       | R9          |

| R10      | R10_fiq  | R10          | R10      | R10      | R10         |

| R11      | R11_fiq  | R11          | R11      | R11      | R11         |

| R12      | R12_fiq  | R12          | R12      | R12      | R12         |

| R13      | R13_fiq  | R13_svc      | R13_abt  | R13_irq  | R13_und     |

| R14      | R14_fiq  | R14_svc      | R14_abt  | R14_irq  | R14_und     |

| R15 (PC) | R15 (PC) | R15 (PC)     | R15 (PC) | R15 (PC) | R15 (PC)    |

#### General Registers and Program Counter Modes

#### **Program Status Registers**

| CPSR | CPSR     | CPSR     | CPSR     | CPSR     | CPSR     |  |

|------|----------|----------|----------|----------|----------|--|

|      | SPSR_fiq | SPSR_svc | SPSR_abt | SPSR_irq | SPSR_und |  |

Basic and Commonly used Instruction Set of ARM in programming

Data Processing Instructions

Move instructions Arithmetic instructions Logical instructions Comparison instructions Multiply instructions

MOV : move

MOV r0, r1; r0 = r1 MOV r0, #5; r0 = 5 MVN : move (negated) MVN r0, r1; r0 = NOT (r1) =~ (r1)

Example 1

PRE: r5 = 5, r7 = 8; MOV r7, r5, LSL #2; r7 = r5 << 2 = r5\*4 POST: r5 = 5, r7 = 20

LSL: logical shift left

x << y, the least significant bits are filled with zeroes LSR: logical shift right: (unsigned) x >> y, the most significant bits are filled with zeroes ASR: arithmetic shift right

(signed) x >> y, copy the sign bit to the most significant bit ROR: rotate right

((unsigned) x >> y) | (x << (32-y))

RRX: rotate right extended

c flag <<31 | (( unsigned) x >> 1) Performs 33-bit rotate, with the CPSR's C bit being inserted above sign bit of the word

Example 2

PRE: r0 = 0x00000000, r1 = 0x80000004 MOV r0, r1, LSL #1 ; r0 = r1 \*2 POST r0 = 0x0000008, r1 = 0x80000004

Dept. of AD, CIT, Gubbi- 572 216

Page No. - 3 -

**Arithmetic Instructions** Syntax: <instruction> {<cond>} {S} Rd, Rn, N N: a register or immediate value ADD : add ADD r0, r1, r2; r0 = r1 + r2 ADC : add with carry ADC r0, r1, r2; r0 = r1 + r2 + C SUB : subtract SUB r0, r1, r2; r0 = r1 - r2 SBC : subtract with carry SUC r0, r1, r2; r0 = r1 - r2 + C -1 **RSB** : reverse subtract RSB r0, r1, r2; r0 = r2 - r1 RSC : reverse subtract with carry RSC r0, r1, r2; r0 = r2 - r1 + C -1 **MUL** : multiply MUL r0, r1, r2; r0 = r1 x r2 MLA : multiply and accumulate MLA r0, r1, r2, r3; r0 = r1 x r2 + r3 Logical Operations Syntax: <instruction> {<cond>} {S} Rd, RN, N N: a register or immediate value AND : Bit-wise and ORR : Bit-wise or EOR : Bit-wise exclusive-or BIC : bit clear BIC r0, r1, r2; r0 = r1 & Not (r2) Example 3: PRE: r1 = 0b1111, r2 = 0b0101 BIC r0, r1, r2; r0 = r1 AND (NOT (r2)) POST: r0=0b1010 **Comparison Instructions** Compare or test a register with a 32-bit value Do not modify the registers being compared or tested But only set the values of the NZCV bits of the Do not need to apply to S suffix for comparison CPSR register. instruction to update the flags in CPSR register Syntax: <instruction> {<cond>} {S} Rd, N N: a register or immediate value CMP: compare CMP r0, r1; compute (r0 - r1) and set NZCV CMN: negated compare

Dept. of AD, CIT, Gubbi- 572 216

Page No. - 4 -

```

CMP r0, r1; compute (r0 + r1) and set NZCV

TST: bit-wise AND test

TST r0, r1; compute (r0 AND r1) and set NZCV

TEQ: bit-wise exclusive-or test

TEQ r0, r1; compute (r0 EOR r1) and set NZCV

Example 4

PRE: CPSR = nzcvqiFt_USER, r0 = 4, r9 = 4

CMP r0, r9

POST: CPSR = nZcvqiFt_USER

Multiply Instruction

Syntax:

MLA{<cond>} {S} Rd, Rm, Rs, Rn

MUL{<cond>} {S} Rd, Rm, Rs

MUL : multiply

MUL r0, r1, r2; r0 = r1*r2

MLA : multiply and accumulate

MLA r0, r1, r2, r3; r0 = (r1*r2) + r3

Syntax: <instruction>{<cond>} {S} RdLo, RdHi, Rm, Rs

Multiply onto a pair of register representing a 64-bit value

UMULL : unsigned multiply long

UMULL r0, r1, r2, r3; [r1,r0] = r2*r3

UMLAL : unsigned multiply accumulate long

UMLAL r0, r1, r2, r3; [r1,r0] = [r1,r0]+(r2*r3)

SMULL: signed multiply long

SMULL r0, r1, r2, r3; [r1,r0] = r2*r3

SMLAL : signed multiply accumulate long

SMLAL r0, r1, r2, r3; [r1,r0] = [r1,r0]+(r2*r3)

Branch Instructions (Cont.)

Syntax

B{<cond>} lable

BL{<cond>} lable

B : branch

B label; pc (program counter) = label Used to change execution flow

BL : branch and link

BL label; pc = label, lr = address of the next address after the BL

Similar to the B instruction but can be used for subroutine

Call Overwrite the link register (lr) with a return address

```

Page No. - 5 -

```

Example 5

B forward

ADD r1, r2, #4

ADD r0, r6, #2

ADD r3, r7, #4

Forward

SUB r1, r2, #4

Backward

SUB r1, r2, #4

B backward

```

Load-Store Instructions

Transfer data between memory and processor registers Three types Single-register transfer Multiple-register transfer Swap

Moving a single data item in and out of register Data item can be A word (32-bits), Halfword (16-bits), Bytes (8-bits) Syntax

<LDR | STR>{<cond>}{B} Rd, addressing1 LDR{<cond>}SB | H | SH Rd, addressing2 STR{<cond>} H Rd, addressing2

LDR : load word into a register from memory

LDRB : load byte

LDRSB : load signed byte

LDRH : load half-word

LSRSH : load signed halfword

STR: store word from a register to memory STRB : store byte

STRH : store half-word

Example 7

LDR r0, [r1] ;= LDR r0, [r1, #0] ;r0 = mem32[r1] STR r0, [r1] ;= STR r0, [r1, #0] ;mem32[r1]= r0 Register r1 is called the base address register

Page No. - 6 -

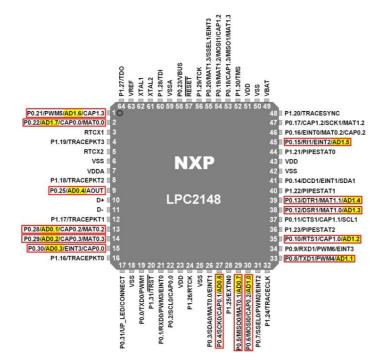

### ARM LPC 2148 FEATURES:

- 16-bit/32-bit ARM7TDMI-S Microcontroller.

- 40 kB of on-chip static RAM and 512 kB of on-chip flash memory.

- In-System Programming/In-Application Programming (ISP/IAP) via onchip boot loader software.

- Embedded ICE RT and Embedded Trace interfaces offer real-time debugging with the on-chip Real Monitor software and high-speed tracing of instruction execution.

- USB 2.0 Full-speed compliant device controller with 2 kB of endpoint RAM.

- Two 10-bit ADCs provide a total of 14 analog inputs

- Single 10-bit DAC provides variable analog output

- Two 32-bit timers/external event counters (with four capture and four compare channels each)

- PWM unit (six outputs)

- Watchdog Timer.

- Low power Real-Time Clock (RTC) with independent power and 32 kHz clock input.

- Multiple serial interfaces including two UARTs, two Fast I<sup>2</sup>C-bus (400 kbit/s), SPI and SSP with buffering and variable data length capabilities.

- Vectored Interrupt Controller (VIC) with configurable priorities and vector addresses.

- 60 MHz maximum CPU clock available from programmable on-chip PLL with settling time of 100 us.

- On-chip integrated oscillator operates with an external crystal from 1 MHz to 25 MHz

- Power saving modes include Idle and Power-down.

- Individual enable/disable of peripheral functions as well as peripheral clock scaling for additional power optimization.

Page No. - 7 -

LPC 2148 TECHNICAL SPECIFICATIONS:

- Microcontroller: LPC2148 with 512K on chip memory

- Crystal for LPC2148: 12Mhz

- Crystal for RTC: 32.768KHz

- 6 10pin Berg headers for external interfacing(GPIOs)

- No separate programmer required (Program with Flash Magic usingonchip boot loader)

- No Separate power adapter required (USB port as power source)

- 20pin(2X10) FRC JTAG connector for Programming and debugging

- 16 Pin Berg Header for LCD Interfacing

- Two RS-232 Interfaces (UART0 and UART1)

- Real-Time Clock with Battery Holder

- 1 Analog Potentiometer connected to ADC

- 4 USER Switches

- 8 USER LEDs

- Reset and Boot loader Switches

- On Board Buzzer Interface

#### HOW TO USE KEIL μVISION4 For ARM7 (LPC2148)

Step By Step

Keil is on the tool which is widely used in Industry, KEIL has tools for ARM, Cortex-M, Cortex-R, 8051, C166, and 251 processor families. In this article we are goin  $\xi$  to discuss KEIL tools for ARM. The development tools of for ARM include following...

- 1. µvision IDE v4

- 2. Compiler for ARM (armcc)

- 3. MicroLib (Clibrary)

- 4. Assembler for ARM (*a*masm)

- 5. Linker For ARM (armLink)

Step1: Click for KEIL  $\mu$ VISION4 Icon . Which appears after Installing Keil KEIL  $\mu$ VISION4. This will open uvison IDE.

## Keil Setup to Generate .Hex File

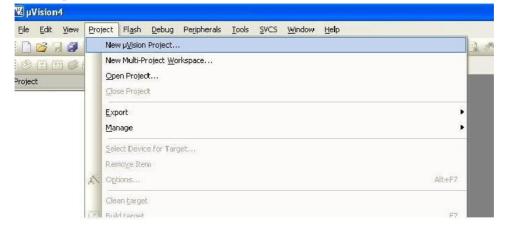

Step2: Click on Project Menu, Then New µVison Project.

Dept. of AD, CIT, Gubbi- 572 216

Page No. - 9 -

#### <u>21CS43, MES-LAB</u>

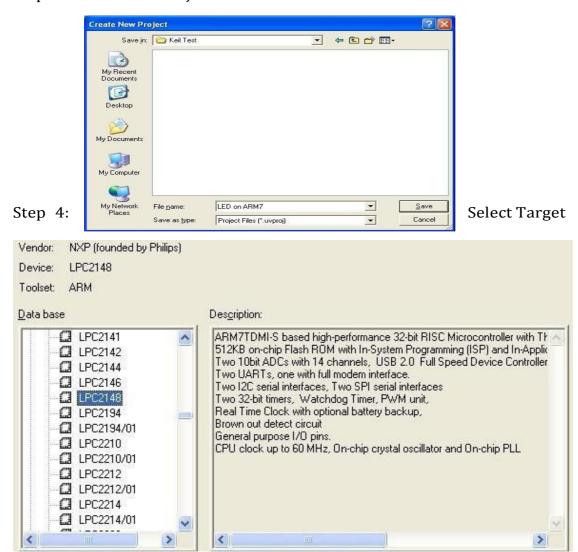

Step3: Create New Project Folder named as "Keil Test".

Device

Step 5: Then select specific chip i.e. LPC2148.

For ALP program, CLICK "NO", For "C" program click on "YES"

| µVision    |                                                                               |              |

|------------|-------------------------------------------------------------------------------|--------------|

| 2          | Copy Philips LPC2100 Startup Code to Project Folder and Add File to Project ? |              |

|            |                                                                               |              |

|            |                                                                               |              |

| Dept. of A | AD, CIT, Gubbi- 572 216                                                       | Page No 10 - |

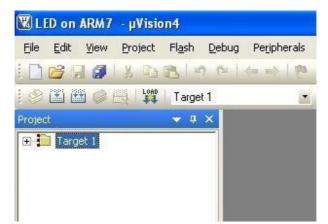

Step 6: Then you will see following window

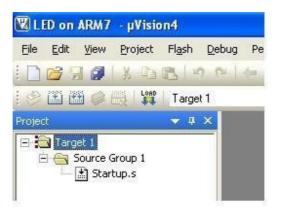

Step 7: Now you see Startup.s is already added which is necessary for running code for Keil.

Note: Code wills Not Run without Startup.s

Startup.s is available in C:\Keil\ARM\Startup\Philips.

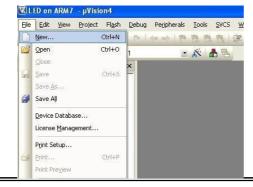

Step 8: Now Click on File Menu and Click on New.

Dept. of AD, CIT, Gubbi- 572 216

Page No. - 11 -

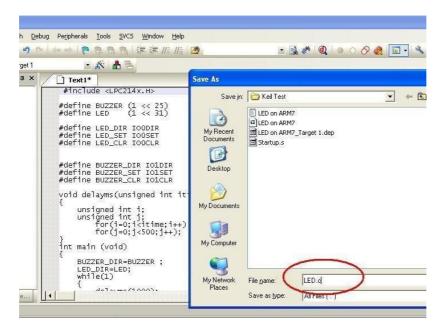

Step 09: Write Code for Blink LED in C OR ASM and FileName.c/ASM Save.

Note: Don't forget to save .c/ASM Extension.

Step 10: Now you Window in C Syntax.

| 🕱 LED on ARM7 - µVision4             |                                          |

|--------------------------------------|------------------------------------------|

| <u>File Edit View Project Fla</u> sh | Debug Peripherals Tools SVCS Window Help |

| i 🗋 🚰 🖫 🏉 i 🐰 🖻 🕮 i 🕫                |                                          |

| i 🔗 🔛 🖽 🥔 拱   🙀   Target             | 1 🔹 🔊 📥 🔁                                |

| Project 🛛 🔻 🕈                        | × LED.c*                                 |

| 🖃 🔁 Target 1                         | 01 #include <lpc214x.h></lpc214x.h>      |

| E 🔄 Source Group 1                   | 02                                       |

| 🔚 🔝 Startup.s                        | 03 #define BUZZER (1 << 25)              |

|                                      | 04 #define LED (1 << 31)                 |

|                                      | 05                                       |

|                                      | 06 #define LED DIR IOODIR                |

Step 11: Now you add LED.c file by adding Source Group 1 Add files to Group 'Source Group 1'.

| 🕱 LED on ARM7 -                  | µVision4                                                   |                |

|----------------------------------|------------------------------------------------------------|----------------|

| <u>Eile E</u> dit <u>V</u> iew E | project Flash Debug Peripherals Tools SVCS                 | <u>W</u> indow |

| i 🗋 🗃 🗑 🖉 🗎                      | N BB I D D I C D I C D B B B B B B B B B B B B B B B B B B | je je //       |

| i 🔗 🖾 🕮 🥔 🖶                      | 📑 🙀 Target 1 🛛 💽 🎊 📥 🔁                                     |                |

| Project                          | • • × 🗋 LED.c*                                             |                |

| 🖃 🛅 Target 1                     | 01 #include <lpc214< td=""><td>łx.H&gt;</td></lpc214<>     | łx.H>          |

| E Source Con                     | Options for Group 'Source Group 1' Alt+F7                  | << 25          |

|                                  | Open File                                                  | << 3:          |

|                                  | Open List File                                             | OODIR          |

|                                  | Open <u>M</u> ap File                                      | OOSET          |

|                                  | Rebuild all target files                                   | - COULIN       |

|                                  | Build target F7                                            | R 1011         |

|                                  | Tr <u>a</u> nslate File                                    | T 101:         |

|                                  | Stop byild                                                 | R 101(         |

|                                  | Add Group                                                  | gned i         |

|                                  | Add Files to Group 'Source Group 1'                        | i;             |

|                                  | Remove Group 'Source Group 1' and its Files                | j;             |

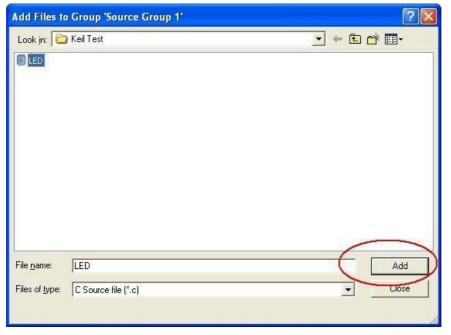

## Step 12: Add LED.C file.

Dept. of AD, CIT, Gubbi- 572 216

Page No. - 13 -

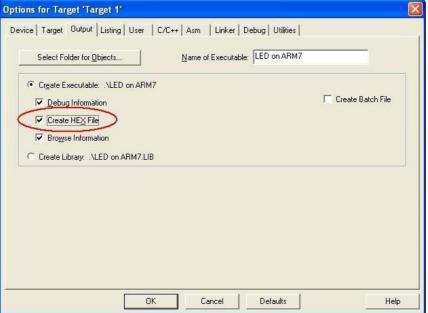

Step 13: Now Click on Options for Target 'Target 1'.

Step 14: Go to Options for Target 'Target 1'. Click on Check Box Create HEX

Step 15: Then go to Linker. Click on Use Memory Layout for Target Dialog.

| evice   Targ                                          | et Output Listing User C/C++ A:       | sm Linker Debug              | Utilities |

|-------------------------------------------------------|---------------------------------------|------------------------------|-----------|

| 🔽 <u>U</u> se Mer                                     | nory Layout from Target Dialog        |                              |           |

| ∏ Ма <u>к</u>                                         | e RW Sections Position Independent    | R/O Base:                    | 0x0000000 |

| ∏ M <u>a</u> ki                                       | e RO Sections Position Independent    | R/W Base                     | 0x4000000 |

| ∏ Do <u>n</u> '                                       | t Search Standard Libraries           | and the second second second | -         |

| 🔽 Repo                                                | ort 'might fail' Conditions as Errors | <u>d</u> isable Warnings:    | 1         |

| Scatter                                               | [                                     |                              |           |

| Scatter<br>File<br><u>M</u> isc<br>controls<br>Linker | -cpu ARM7TDMI *.ostrictscatter ''LE   | D on 4BM7 set"               |           |

Dept. of AD, CIT, Gubbi- 572 216

Page No. - 14 -

| 🕱 LED on ARM7 - µVision4                 |                                                                                                                                                                                                                     |

|------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <u>File Edit View Project Flash D</u> eb | ug Pe <u>r</u> ipherals <u>T</u> ools <u>S</u> VCS <u>W</u> indow <u>H</u> elp                                                                                                                                      |

| DE RANK DE P                             | 今    ● ● ● ● ● ●                                                                                                                                                                                                    |

| 🗄 🍪 🏋 🎦 😂 🔣 🖓 🎝 Target 1                 | 🔹 🔊 📥 🔁                                                                                                                                                                                                             |

| Project Rebuild                          | LED.c                                                                                                                                                                                                               |

| Rebuild all target files                 | <pre>01 #include <lpc214x.h> 02 03 #define BUZZER (1 &lt;&lt; 25) 04 #define BUZZER_DIR IO1DIR 05 #define BUZZER_SET IO1SET 06 #define BUZZER_CLR IO1CLR 07 08 void delayms(unsigned int iti 09 {</lpc214x.h></pre> |

|                                          | 10         unsigned int i;           11         unsigned int j;           12         for(i=0;i <itime;i++)< td="">           13         for(j=0;j&lt;500;j++);</itime;i++)<>                                        |

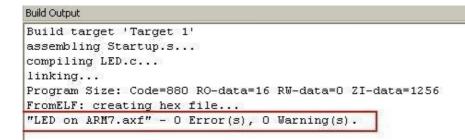

Step 16: Then Click on Rebuild All Target Files

Step 17: Now you see 0 Error(s), 0 Warning (s). Then Hex File will create in Specific Folder. Now to download it for you target hardware.

## Part A

## Program1-Sample Programs using Keil Compiler:

<u>AIM: To write and simulate ARM assembly language programs for data</u> <u>transfer, arithmetic and logical operations (Demonstrate with the help of a</u> <u>suitable program).</u>

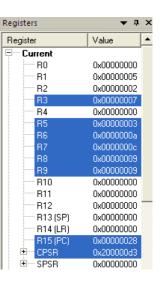

1. Data Transfer.

The below assembly level program moves the 32 bit data from register to register.

area movt, code, readonly entry mov r1,#0005 ; Mov immediate 32 bit data to r1 mov r2,#0002 ; Mov immediate 32 bit data to r1 mov r3,r1 ; Register-Register movement mov r4,r2 ; Register-Register movement

stop b stop end ; End of the program

Registers Value Register Current 0x00000000 R0 0x00000005 R1 0x00000002 R2 R3 0x00000005 R4 0x00000002 R5 0x00000000 R6 0x00000000 **B**7 0x00000000 **B**8 0×00000000 **B**9 0×00000000 B10 0×00000000 0×00000000 B11 0×00000000 B12 R13 (SP) 0x00000000 R14 (LR) 0x00000000 R15 (PC) 0x00000010 CPSR 0x000000d3 ÷ SPSR 0x00000000

2. Arithmetic Operations

A. Addition, Subtraction and Multiplication:

| area addt, code, rea<br>entry | adonly                                    |

|-------------------------------|-------------------------------------------|

| mov r1,#0005                  | ; Mov immediate 32 bit data to r1         |

| mov r2,#0002                  | ; Mov immediate 32 bit data to r2         |

| add r3,r2,r1                  | ; Add the contents present in r2 with the |

|                               | contents of r1 and store in r3            |

| sub r5,r1,r2                  | ; Subtract; r5 = r1-r2                    |

| mul r6,r1,r2                  | ; Multiply                                |

| mov r7,r6                     |                                           |

| add r7,#2                     | ; Add immediate data                      |

| mov r8,r7                     |                                           |

| sub r8,#3                     | ; Subtract immediate data                 |

| mov r9,r8                     |                                           |

stop b stop

end

mov r0,#0x83 mov r1,r0

mov r2, r1

lsr r2, #4 mov r3, r0 and r3, # 0X0f and r1,r0 orr r2.r1

lsr r2, #3

end

stop b stop

| Registers                     | <b>▼</b> ₽ | 2 |

|-------------------------------|------------|---|

| Register                      | Value      | 4 |

| Current                       |            |   |

| R0                            | 0x00000083 |   |

| <mark>-</mark> <mark>-</mark> | 0x00000080 |   |

| R2                            | 0x00000008 |   |

| R3                            | 0x00000003 |   |

| R4                            | 0x00000000 |   |

| R5                            | 0x00000000 |   |

| R6                            | 0x00000000 |   |

| B7                            | 0x00000000 |   |

| R8                            | 0x00000000 |   |

| R9                            | 0x00000000 |   |

| R10                           | 0x00000000 |   |

| R11                           | 0x00000000 |   |

| R12                           | 0x00000000 | _ |

| R13 (SP)                      | 0x00000000 |   |

| R14 (LR)                      | 0x00000000 |   |

| R15 (PC)                      | 0x0000001c |   |

| 🛨 🗠 CPSR                      | 0x000000d3 |   |

| 主 🗠 SPSR                      | 0x00000000 |   |

3. Logical operations : To perform AND, Logical Shift operations, area dis,code,readonly entry

; Perform Logical right Shift operation

; Logical shift right r2 by 3 bit positions

and r1, # 0Xf0; Perform Logical AND operation

Write an ALP using ARM to execute the following instructions

; Logical OR Operation

• ADD r1, r0, r0, LSL #3 ; r1 = r0 + r0 << 3 = r0 + 8 × r0

• ADD r1, r0, r0, LSR #3 ; r1 = r0 + r0 >> 3 = r0 + r0/8 (unsigned)

• ADD r1, r0, r0, ASR #3 ; r1 = r0 + r0 >> 3 = r0 + r0/8 (signed)

The state of the system after loading the code for Program 1

- ✓ The semicolon indicates a user-supplied comment.

- ✓ Anything following a semicolon on the same line is ignored by the assembler.

- ✓ The first line is AREA Example1, CODE, READONLY is an assembler directive and is required to set up the program. It is a feature of the development system and not the ARM assembly language.

- ✓ An assembler from a different company may have a different way of defining the start of a program. In this case, AREA refers to the segment of code, Example1 is the name we've given it, CODE indicates executable code rather than data, and READONLY state that it cannot be modified at run time.

Dept. of AD, CIT, Gubbi- 572 216

Page No. - 17 -

- ✓ Anything starting in column 1 (in this case Stop) is a label that can be used to refer to that line.

- ✓ The instruction Stop B Stop means 'Branch to the line labeled Stop' and is used to create an infinite loop. This is a convenient way of ending programs in simple examples like these.

- ✓ The last line END is an assemble directive that tells the assembler there is not more code to follow. It ends the program.

#### Graded ARM assembly language Examples

#### ADDITION

The problem: P = Q + R + SLet Q = 2, R = 4, S = 5. Assume that r1 = Q, r2 = R, r3 = S. The result Q will go in r0.

The Code

ADD r0,r1,r2 ;add Q to R and put in P ADD r0,r0,r3 ;add S to P and put the result in P

```

The program

AREA Example1, CODE, READONLY

ADD r0,r1,r2

ADD r0,r3

Stop B Stop

END

```

Notes:

The semicolon indicates a user-supplied comment. Anything following a semicolon on the same line is ignored by the assembler.

The first line is AREA Example1, CODE, READONLY is an assembler directive and is required to set up the program. It is a feature of the development system and not the ARM assembly language. An assembler from a different company may have a different way of defining the start of a program. In this case, AREA refers to the segment of code, Example1 is the name we've given it, CODE indicates executable code rather than data, and READONLYstate that it cannot be modified at run time.

Anything starting in column 1 (in this case Stop) is a label that can be used to refer to that line.

The instruction Stop B Stop means 'Branch to the line labelled Stop' and is used to create an infinite loop. This is a convenient way of ending programs in simple examples like these.

The last line ENDis an assemble directive that tells the assembler there is not more code to follow. It ends the program.

Page No. - 18 -

|                                                    |                                                                                                          | Mexamples\Example1_ADDITION.uvproj - µVision                                                                                                                                                       |                                                                                 |

|----------------------------------------------------|----------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------|

| <u>File Edit V</u> iew                             | <u>Project</u> Fl <u>a</u> sh <u>I</u>                                                                   | ebug Pe <u>r</u> ipherals <u>T</u> ools <u>S</u> VCS <u>W</u> indow <u>H</u> elp                                                                                                                   |                                                                                 |

| 🗋 🚰 🛃 🗿                                            | 多時間 つく                                                                                                   | -   <= ->   習 魯 魯 魯   譯 譯 /// /版   🌌                                                                                                                                                               |                                                                                 |

| 👫 🖹 🛞 🤾                                            | } () +() +() ↓()                                                                                         | N 🔄 📰 🖧 🐺 • 💷 • 🕎 • 🔜 •                                                                                                                                                                            | · 🔳 • 🔆 • 📃                                                                     |

| Registers                                          | Ф                                                                                                        | × Disassembly                                                                                                                                                                                      | φ X                                                                             |

| Register                                           | Value                                                                                                    | 2: ADD r0,r1,r2                                                                                                                                                                                    | <b></b>                                                                         |

|                                                    | 10.00                                                                                                    | 0x00000000 E0810002 ADD                                                                                                                                                                            | R0,R1,R2                                                                        |

| R0<br>R1<br>R2<br>R3<br>R4<br>R5<br>R6<br>R7<br>R8 | 0x0000000B<br>0x00000002<br>0x00000004<br>0x00000005<br>0x00000000<br>0x0000000<br>0x0000000<br>0x000000 | 3: ADD r0,r3<br>0x00000004 E0800003 ADD<br>4: Stop B Stop<br>→ 0x00000008 EAFFFFE B<br>0x0000000 0000000 ANDEQ<br>0x00000014 0000000 ANDEQ<br>0x00000018 0000000 ANDEQ<br>0x00000018 0000000 ANDEQ | R0, R0, R3<br>0x0000008<br>R0, R0, R0<br>R0, R0, R0<br>R0, R0, R0<br>R0, R0, R0 |

| R9<br>R10<br>R11<br>R12<br>R13 (SP)<br>R14 (LR)    | 0x00000000<br>0x00000000<br>0x00000000<br>0x000000                                                       | Example1_ADDITION.s      AREA Example1, CODE, F     ADD r0,r1,r2     ADD r0,r3     Stop B Stop     END                                                                                             | READONLY                                                                        |

Figure Example 1.1 The state of the system after loading the code for Example 1

Note that the contents of r0 are 2 + 4 + 5 = 11 = 0x0B. This is the result we expected.

#### Example 2 ADDITION

This problem is the same as Example 1. P = Q + R + SOnce again, let Q = 2, R = 4, S = 5 and assume r1 = Q, r2 = R, r3 = S. In this case, we will put the data in memory in the form of constants before the program runs. The Code MOV r1,#Q ;load Q into r1 MOV r2,#R ;load R into r2 MOV r3,#S ;load S into r3 ADD r0,r1,r2 ;Add Q to R ADD r0,r0,r3 ;Add S to (Q + R) Here we use the instruction MOV that copies a value into a register. The value may be the contents of another register or a literal. The literal is

denoted by the # symbol.

We can write, for example, MOV r7,r0, MOV r1,#25 or MOV r5,#Time

Dept. of AD, CIT, Gubbi- 572 216

Page No. - 19 -

We have used symbolic names Q, R and S. We have to relate these names to actual values. We do this with the EQU (equate) assembler directive; for example, Q EQU 2 Relates the name Q to the value 5. If the programmer uses Q in an expression, it is exactly the same as writing 2. The purpose of using Q rather than 2 is to make the program more readable. The program AREA Example2, CODE, READONLY MOV r1,#Q ;load r1 with the constant Q MOV r2,#R MOV r3,#S ADD r0,r1,r2 ADD r0,r0,r3 Stop B Stop Q EQU 2 ;Equate the symbolic name Q to the value 2 R EQU 4 ; SEQU5; **END**

#### **Example 3 ADDITION**

The problem once again is P = Q + R + S. As before, Q = 2, R = 4, S = 5 and we assume that r1 = Q, r2 = R, r3 = S.

In this case, we will put the data in memory as constants before the program runs. We first use the load register,

LDR r1,Q instruction to load register r1 with the contents of memory location Q. This instruction *does not exist* and is not part of the ARM's instruction set. However, the ARM assembler automatically changes it into an actual instruction.

We call LDR r1,Q a *pseudoinstruction* because it behaves like a real instruction. It is indented to make the life of a programmer happier by providing a shortcut.

The Code LDR r1,Q ;load r1 with Q LDR r2,R ;load r2 with R LDR r3,S ;load r3 with S ADD r0,r1,r2 ;add Q to R ADD r0,r0,r3 ;add in S STR r0,Q ;store result in Q The program AREA Example3, CODE, READWRITE LDR r1,Q ;load r1 with Q LDR r2,R ;load r2 with R LDR r3,S ;load r3 with S

Dept. of AD, CIT, Gubbi- 572 216

Page No. - 20 -

<u>21CS43, MES-LAB</u>

ADD r0,r1,r2 ;add Q to R ADD r0,r3 ;add in S STR r0,Q ;store result in Q Stop B Stop AREA Example3, CODE, READWRITE P SPACE 4 ;save one word of storage Q DCD 2 ;create variable Q with initial value 2 R DCD 4 ;create variable R with initial value 4 S DCD 5 ;create variable S with initial value 5 END

Note how we have to create a data area at the end of the program. We have reserved spaces for P, Q, R, and S. We use the SPACE directive for S to reserve 4 bytes of memory space for the variable S. After that we reserve space for Q, R, and S. In each case we use a DCD assembler directive to reserve a word location (4 bytes) and to initialize it. For example,

Q DCD 2 ;create variable Q with initial value 2 means 'call the current line Q and store the word 0x0000002 at that location.

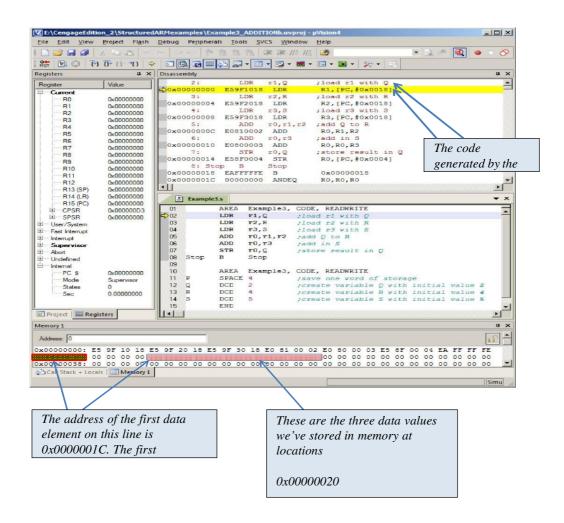

Figure Example 3.1 shows the state of the program after it has been loaded. In this case we've used the view memory command to show the memory space. We have highlighted the three constants that have been pre-loaded into memory.

Take a look at the disassembled code. The pseudoinstruction LDR r1,Q was actually translated into the real ARM instruction LDR r1,[PC,#0x0018]. This is still a load instruction but the addressing mode is register indirect. In this case, the address is the contents of the program counter, PC, plus the hexadecimal offset 0x18. Note also that the program counter is always 8 bytes beyond the address of the current instruction. This is a feature of the ARM's pipeline.

Consequently, the address of the operand is [PC] + 0x18 + 8 = 0 + 18 + 8 = 0x20.

If you look at the memory display area you will find that the contents of 0x20 are indeed 0x00000002.

Dept. of AD, CIT, Gubbi- 572 216

Page No. - 21 -

Figure The state of the system after loading the program

#### Example 4 ADDITION

The problem P = Q + R + S where Q = 2, R = 4, S = 5. In this case we are going to use register indirect addressing to access the variables. That is, we have to set up a pointer to the variables and access them via this pointer. The Code ADR r4,TheData ;r4 points to the data area LDR r1,[r4,#Q] ;load Q into r1 LDR r2,[r4,#R] ;load R into r2 LDR r3,[r4,#S] ;load S into r3 ADD r0,r1,r2 ;add Q and R ADD r0,r0,r3 ;add S to the total STR r0,[r4,#P] ;save the result in memory

Dept. of AD, CIT, Gubbi- 572 216

Page No. - 22 -

#### <u>21CS43, MES-LAB</u>

The program AREA Example4, CODE, READWRITE **ENTRY** ADR r4, The Data ; r4 points to the data area LDR r1,[r4,#Q] ;load Q into r1 LDR r2,[r4,#R] ;load R into r2 LDR r3,[r4,#S] ;load S into r3 ADD r0,r1,r2 ;add Q and R ADD r0,r0,r3 ;add S to the total STR r0,[r4,#P] ;save the result in memory Stop B Stop P EQU 0 ;offset for P Q EQU 4 ;offset for Q R EQU 8 ;offset for R S EOU 12 ;offset for S AREA Example4, CODE, READWRITE TheData SPACE 4 ;save one word of storage for P DCD 2 ;create variable Q with initial value 2 DCD 4 ;create variable R with initial value 4 DCD 5 ;create variable S with initial value 5 **END**

Figure Example 4.1 shows the state of the system after the program has been loaded. I have to admit, that I would not write this code as it is presented. It is far too verbose. However, it does illustrate several concepts.

First, the instruction ADR r4,TheData loads the address of the data region (that we have labelled TheData into register r4. That is, r4 is pointing at the data area. If you look at the code, we have reserved four bytes for P and then have loaded the values for Q, R and S into consecutive word location. Note that we have not labelled any of these locations.

The instruction ADR (load an address into a register) is a pseudoinstruction. If you look at the actual disassembled code in Figure Example 4.1 you will see that this instruction is translated into ADD r4,pc,#0x18. Instead of loading the actual address of TheData into r4 it is loading the PC plus an offset that will give the appropriate value. Fortunately, programmers can sleep soundly without worrying about how the ARM is going to translate an ADR into actual code – that's the beauty of pseudoinstructions.

When we load Q into r1 we use LDR r1,[r4,#Q]. This is an ARM load register instruction with a literal offset; that is, Q. If you look at the EQU region, Q is equated to 4 and therefore register r1 is loaded with the data value that is 4 bytes on from where r4 is pointing. This location is, of course, where the data corresponding to Q has been stored.

Page No. - 23 -

| ile <u>E</u> dit <u>V</u> iew | Project Flash De         |                                                                                                                                               |               |

|-------------------------------|--------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|---------------|

| 🗋 💕 🛃 🥥                       | と中間 うら                   | 🕘 🗠 🦉 🦉 🤹 🧱 🚛 🎼 🌌 📃 🔹 🔍 🖉                                                                                                                     | 4             |

| 👬 🗉 🚳 🕅                       | 🖓 🖓 😗 🏟                  | 2 🕼 🖬 🛤 🖓 v 💷 v 🐷 v 🔝 v 🧏 v 🖂                                                                                                                 |               |

| gisters                       | фX                       | Disassembly                                                                                                                                   | <b>д &gt;</b> |

| Register                      | Value                    | 3: ADR r4, TheData ;r4 points to the data area                                                                                                | 4             |

| Current                       |                          | C>0x00000000 E28F4018 ADD R4, PC, #0x00000018                                                                                                 |               |

| R0                            | 0x0000000                | 4: LDR r1,[r4, #Q] ;load Q into r1<br>0x00000004 E5941004 LDR R1.[R4, #0x0004]                                                                |               |

| R1                            | 0x0000000                |                                                                                                                                               |               |

| R2                            | 0x0000000                | 5: LDR r2,[r4,#R] ;load R into r2<br>0x00000008 E5942008 LDR R2,[R4,#0x0008]                                                                  |               |

| R3                            | 0x0000000                | 6: LDR r3, [r4, #5] ;load S into r3                                                                                                           |               |

| R4<br>R5                      | 0x00000000               | 0x0000000C E594300C LDR R3,[R4,#0x000C]                                                                                                       |               |

| R5<br>R6                      | 0x00000000<br>0x00000000 | 7: ADD r0,r1,r2 ;add Q and R                                                                                                                  |               |

|                               | 0x00000000               | 0x0000010 E0810002 ADD R0,R1,R2                                                                                                               |               |

|                               | 0x00000000               | 8: ADD r0,r0,r3 ;add S to the total                                                                                                           |               |

|                               | 0x00000000               | 0x00000014 E0800003 ADD R0,R0,R3                                                                                                              |               |

| R10                           | 0x0000000                | 9: STR r0,[r4,#P] ;save the result in memory                                                                                                  |               |

| R11                           | 0x0000000                | 0x0000018 E5840000 STR R0,[R4]                                                                                                                |               |

| R12                           | 0x0000000                | 10: Stop B Stop<br>0x000001C EAFFFFE B 0x000001C                                                                                              |               |

| R13 (SP)                      | 0x0000000                | 0x00000020 00000000 ANDEQ R0,R0,R0                                                                                                            |               |

| R14 (LR)                      | 0x0000000                | 0x00000024 00000002 ANDEQ R0,R0,R2                                                                                                            |               |

| R15 (PC)                      | 0x0000000                | 0x00000028 00000004 ANDEQ R0,R0,R4                                                                                                            |               |

| E CPSR                        | 0x00000003<br>0x00000000 | 0x0000002C 00000005 ANDEQ R0,R0,R5                                                                                                            |               |

| User/System                   | 0x0000000                |                                                                                                                                               | E F           |

| ···· Fast Interrupt           |                          |                                                                                                                                               |               |

| ··· Interrupt                 |                          | Example4.s                                                                                                                                    | <b>*</b> >    |

| Supervisor                    |                          | 01 AREA Example4, CODE, READWRITE                                                                                                             | -             |

| Abort                         |                          | 02 ENTRY                                                                                                                                      |               |

| Undefined                     |                          | CO3         ADR         r4, TheData         ;r4 points to the data area           04         LDR         r1, [r4, ‡0]         :load 0 into r1 |               |

| PC S                          | 0x00000000               | 05 LDR r2, [r4, #R] ; load g into r2                                                                                                          |               |

| Mode                          | Supervisor               | 06 LDR r3, [r4, #S] ; load S into r3                                                                                                          |               |

| States                        | 0                        | 07 ADD r0, r1, r2 ; add 0 and R                                                                                                               |               |

| Sec                           | 0.00000000               | 08 ADD r0,r0,r3 ;add S to the total                                                                                                           |               |

|                               |                          | 09 STR r0,[r4, #P] ;save the result in memory                                                                                                 |               |

|                               |                          | 10 Stop B Stop                                                                                                                                |               |

|                               |                          | 11                                                                                                                                            |               |

|                               |                          | 12 P EQU 0 :offset for P<br>13 Q EQU 4 :offset for O                                                                                          |               |

|                               |                          | 13 Q EQU 4 ;offset for Q<br>14 R EQU 8 ;offset for R                                                                                          |               |

|                               |                          | 15 S EQU 12 ;offset for S                                                                                                                     |               |

|                               |                          | 16                                                                                                                                            |               |

|                               |                          | 17 AREA Example4, CODE, READWRITE                                                                                                             |               |

|                               |                          | 18 TheData SPACE 4 ;save one word of storage for P                                                                                            |               |

|                               |                          | 19 DCD 2 ;create variable Q with initial value                                                                                                |               |

|                               |                          | 20 DCD 4 ;create variable R vith initial value                                                                                                |               |

|                               |                          | 21 DCD 5 ;create variable S vith initial value<br>22 END                                                                                      | 5             |

| 1                             |                          |                                                                                                                                               |               |

| Project Regi                  | sters                    |                                                                                                                                               | •             |

| mory 1                        |                          |                                                                                                                                               | <b>д</b> ,    |

| ddress: 0                     |                          |                                                                                                                                               | <u>_</u>      |

| 00000000: E                   | 2 8F 40 18 E5            | 94 10 04 E5 94 20 08 E5 94 30 0C E0 81 00 02 E0 80 00 03 E5 84 00 00 EA                                                                       | FF FF         |

|                               |                          | 00 00 02 00 00 00 04 00 00 05 00 00 00 00 00 00 00 00 00 00                                                                                   |               |

|                               |                          | 00 00 00 00 00 00 00 00 00 00 00 00 00                                                                                                        |               |

|                               |                          | <u> </u>                                                                                                                                      | 00 00 2       |

|                               | ls 🔜 Memory 1            |                                                                                                                                               |               |

Figure Example 4.1 The state of the system after loading the program

Figure Example 4.2 The state of the system after executing the program

|                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | <u>_     ×</u> |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

| Eile Edit View                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                  | ebug Peripherals Tools SVCS Window Help                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                |

|                                                                                                                                                                                                                                                                                                                                                                                                      | 3 - 6 - 6 - 7 - 7                                                                | < <   ② ● ● ② ● ● ● ③ ◆ ● ● ○ ◎ ●                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | •              |

| 87 🖪 🛇 🥂                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                |

| egisters                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Ф ×            |

| Register<br>Current                                                                                                                                                                                                                                                                                                                                                                                  | Value                                                                            | 3: ADR r4, TheData ;r4 points to the data area<br>0x00000000 E28F4018 ADD R4, PC, #0x00000018                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | -              |

| Current           R0           R1           R2           R3           R4           R5           R6           R7           R8           R9           R10           R11           R12           R13 (SP)           R14 (LR)           R15 (PC)           R15 (PC)           B- CFSR           B- SPSR           B- Interrupt           B- Modefined           Interrupt           States           Sec | 0x0000000B<br>0x00000002<br>0x00000005<br>0x00000005<br>0x00000000<br>0x00000000 | 4:       LDR       ri, [r4,40]       :load Q into ri         0x00000004       E5941004       LDR       Rl, [R4,40x0004)         0:       S:       LDR       r2, [r4,48]       :load R into r2         0:x00000005       E5942005       LDR       R2, [R4,40x0006]         6:       LDR       r2, [r4,45]       :load S into r3         0:x00000005       E5943005       LDR       R3, [R4,40x0006]         7:       ADD       r0, r1, r2       :add Q and R         0:x00000016       E5840000       STR       R0, R0, R3         9:       STR       r0, [r4,47]       :save the result in memory         0:x00000016       E5840000       STR       R0, R0, R3         9:       STR       r0, [r4,47]       :save the result in memory         0:x00000016       E5840000       ANDE R0, R0, R3         0:x00000020       00000005       ANDEQ R0, R0, R11         0:x00000020       00000005       ANDEQ R0, R0, R4         0:x00000020       00000005       ANDEQ R0, R0, R5         4       Example4, CODE, READWRITE       1         0:       ANR r4, TheData rr4 points to the data area         04       LDR r1, [r4,42] rload 0 into r1       1         05< | × ×            |

| <b>1</b> 0 · · · · · · · · · · · · · · · · · · ·                                                                                                                                                                                                                                                                                                                                                     |                                                                                  | 22 END                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                |

| 🛯 Project 🛛 🧱 Reg                                                                                                                                                                                                                                                                                                                                                                                    | isters                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                |

| emory 1                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | <b>д х</b>     |

| Address: 0                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | <u>_</u>       |

| 0000001F: FI<br>0000003E: 0                                                                                                                                                                                                                                                                                                                                                                          | E 00 00 00 0B<br>0 00 00 00 00<br>0 00 00 00 00                                  | 94 10 04 E5 94 20 08 E5 94 30 0C E0 81 00 02 E0 80 00 03 E5 84 00 00 EA FF<br>00 00 00 02 00 00 00 04 00 00 00 05 00 00 00 00 00 00 00 00 00                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 00             |

| a and a state of the                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                  | Simulation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                |

#### Example 5 ADDITION

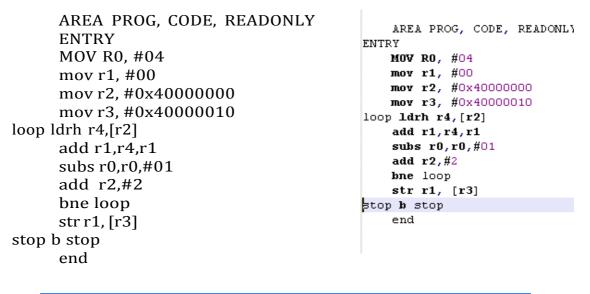

We're going to repeat the same example once again. This time we will write the program in a more compact fashion,

still using the ADR (load register with address instruction).

To simplify the code, we've used simple numeric offsets (because there is relatively little data and the user comments

tell us what's happening. Note that we have used labels Q, R, and S for the data. These labels are redundant and are not

needed since they are not referred to anywhere else in the program. There's nothing wrong with this. These labels just